# VFTV010R013NA

# **Datasheet**

#### **General Description**

The VFTV010R013NA is high voltage MOSFET utilizes charge balance technology to achieve outstanding low on-resistance and lower gate charge. It is engineered to minimize conduction loss, provide superior switching performance and robust avalanche capability. The VFTV010R013NA is optimized for extreme switching performance to minimize switching loss. It is tailored for high power density applications to meet the highest efficiency standards.

### **Symbol**

Figure 1 Symbol of VFTV010R013NA

#### **Features**

- $R_{DS(ON)_{max}} = 1.3 \text{m}\Omega @V_{GS} = 10V$

- Surface-mounted package

- Advanced trench cell design

- 100% UIS and Rg Tested

## **Application**

- Battery Management System

- Machine Tool

- High Power inverter system

### Package Type

Figure 2 Package Type of VFTV010R013NA

## **Ordering Information**

| Product Name  | Package |  |  |

|---------------|---------|--|--|

| VFTV010R013NA | TOLL    |  |  |

## Absolute Maximum Ratings (T<sub>J</sub>= 25 °C, unless otherwise specified)

| Parameter                             |                                | Symbol           | Rating     | Unit |  |

|---------------------------------------|--------------------------------|------------------|------------|------|--|

| Drain-Source Voltage                  |                                | $V_{ m DSS}$     | 100        | V    |  |

| Gate-Source Voltage                   |                                | $V_{GSS}$        | ±20        | V    |  |

| Continuous Drain Current Note 1       | T <sub>C</sub> =25°C           | т                | 395        | Α    |  |

|                                       | $T_{\rm C}=100^{\rm o}{\rm C}$ | $I_{D}$          | 250        | A    |  |

| Pulsed Drain Current Tested           | T <sub>C</sub> =25°C           | $I_{DM}$         | 987        | A    |  |

| Continuous Diode Forward Current      | T <sub>C</sub> =25°C           | $I_{S}$          | 85         | A    |  |

| Max Power Dissipation                 | T <sub>C</sub> =25°C           | D                | 313        | 117  |  |

|                                       | T <sub>C</sub> =100°C          | P <sub>D</sub>   | 125        | W    |  |

| Continuous Drain Current Note 2       | T <sub>A</sub> =25°C           | т                | 40         |      |  |

|                                       | T <sub>A</sub> =70°C           | $I_{D}$          | 32         | A    |  |

| Note:                                 | T <sub>A</sub> =25°C           | D                | 3.1        | 117  |  |

| Max Power Dissipation Note2           | T <sub>A</sub> =70°C           | P <sub>D</sub>   | 2          | W    |  |

| Avalanche Current, Single pulse Note3 | L=0.1mH                        | т                | 100        |      |  |

|                                       | L=0.5mH                        | I <sub>AS</sub>  | 55         | A    |  |

| Avalanche Energy, Single Pulse Note 3 | L=0.1mH                        | Б                | 500        | Т    |  |

|                                       | L=0.5mH                        | $E_{AS}$         | 152        | mJ   |  |

| Max Junction temperature              |                                | $T_{J}$          | 150        | 0.0  |  |

| Storage Temperature Range             |                                | T <sub>STG</sub> | -55 to 150 | °C   |  |

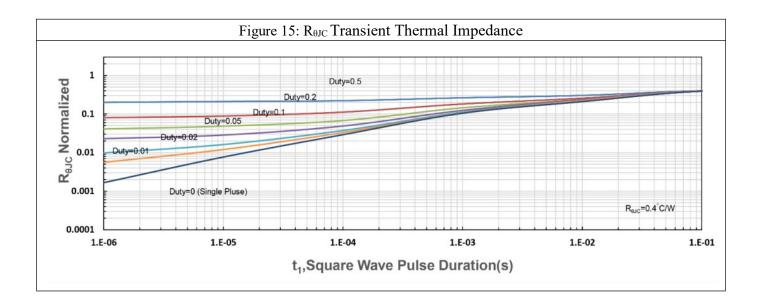

### **Thermal Resistance**

| Parameter                                                | Symbol         | Min | Тур | Max | Unit |  |

|----------------------------------------------------------|----------------|-----|-----|-----|------|--|

| Thermal Resistance, Junction-to-Case                     | $R_{	heta JC}$ |     | 0.4 |     | 9C/W |  |

| Thermal Resistance, Junction-to-Ambient <sup>Note2</sup> | $R_{	heta JA}$ |     | 40  |     | °C/W |  |

#### Notes:

- 1) Max. current is limited by max. junction temperature.

- 2) Surface Mounted on 1in<sup>2</sup> FR-4 board with 1oz

- 3) UIS tested and pulse width are limited by maximum junction temperature 150°C

### VFTV010R013NA

## Electrical Characteristics(T<sub>J</sub>= 25 °C, unless otherwise specified)

| Parameter                               | Symbol              | <b>Test Conditions</b>                                   | Min | Тур   | Max  | Unit      |

|-----------------------------------------|---------------------|----------------------------------------------------------|-----|-------|------|-----------|

| Statistic Characteristics               |                     |                                                          |     |       |      |           |

| Drain-Source Breakdown Voltage          | BV <sub>DSS</sub>   | V <sub>GS</sub> =0V, I <sub>D</sub> =250uA               | 100 |       |      | V         |

| Zero Gate Voltage Drain Current         | I <sub>DSS</sub>    | $V_{DS}$ =80V, $V_{GS}$ =0V                              |     |       | 1    | uA        |

| Gate-Body Leakage Current               | I <sub>GSS</sub>    | $V_{GS}=\pm20V, V_{DS}=0V$                               |     |       | ±100 | nA        |

| Gate Threshold Voltage                  | V <sub>GS(TH)</sub> | V <sub>DS</sub> =V <sub>GS</sub> , I <sub>D</sub> =250uA | 2.0 |       | 4.0  | V         |

| Static Drain-Source On-Resistance Note4 | R <sub>DS(ON)</sub> | V <sub>GS</sub> =10V, I <sub>D</sub> =30A                |     | 1.05  | 1.3  | $m\Omega$ |

| Forward Transconductance                | gfs                 | V <sub>DS</sub> =5V, I <sub>DS</sub> =50A                |     | 108   |      | S         |

| Gate Resistance                         | $R_{G}$             | V <sub>GS</sub> =0V, V <sub>DS</sub> =0V<br>Freq=1MHz    |     | 1.7   |      | Ω         |

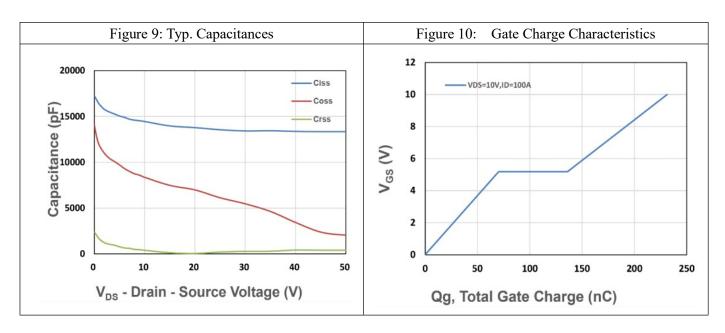

| <b>Dynamic Characteristics</b>          |                     |                                                          |     |       |      |           |

| Input Capacitance                       | C <sub>ISS</sub>    | V <sub>DS</sub> =50V                                     |     | 13000 |      |           |

| Output Capacitance                      | Coss                | $V_{GS}=0V$                                              |     | 2147  |      | pF        |

| Reverse Transfer Capacitance            | $C_{RSS}$           | f=1MHz                                                   |     | 398   |      |           |

| Turn-on Delay Time                      | t <sub>d(on)</sub>  | $V_{DS}=50V$                                             |     | 27.7  |      |           |

| Turn-on Rise Time                       | t <sub>r</sub>      | $I_{DS}=1A$                                              |     | 21.5  |      |           |

| Turn-off Delay Time                     | t <sub>d(off)</sub> | $R_{\text{GEN}}=1\Omega$                                 |     | 89.6  |      | ns        |

| Turn-off Fall Time                      | $t_{\mathrm{f}}$    | $V_{\text{GEN}}=10V$                                     |     | 96.8  |      |           |

| <b>Gate Charge Characteristics</b>      |                     |                                                          |     |       |      |           |

| Gate to Source Charge                   | Qgs                 | V <sub>GS</sub> =10V                                     |     | 70.2  |      | nC        |

| Gate to Drain Charge                    | $Q_{\mathrm{gd}}$   | $V_{DS}=50V$                                             |     | 65.7  |      |           |

| Gate Charge Total                       | Qg                  | $I_{D}=100A$                                             |     | 231   |      |           |

| <b>Reverse Diode Characteristics</b>    |                     |                                                          |     |       |      |           |

| Diode Forward Voltage Note5             | $V_{SD}$            | V <sub>GS</sub> =0V, I <sub>SD</sub> =30A                |     | 0.75  | 1.1  | V         |

| Reverse Recovery Time                   | t <sub>rr</sub>     | $I_{DS}$ =30A, $V_{GS}$ =0V                              |     | 120   |      | ns        |

| Reverse Recovery Charge                 | Qrr                 | di/dt=100A/us                                            |     | 400   |      | nC        |

<sup>4)</sup> Pulse test (pulse width<=300us, duty cycle<=2%)

<sup>5)</sup> Guaranteed by design, not subject to production testing.

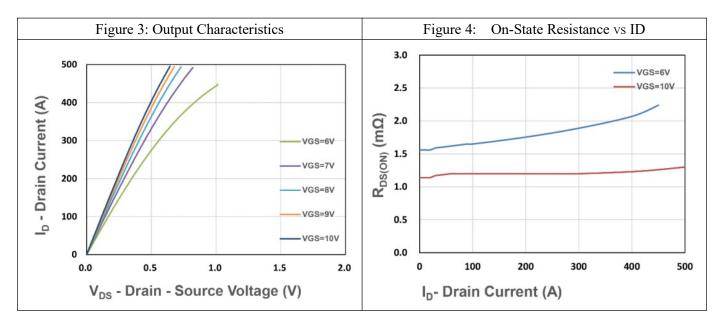

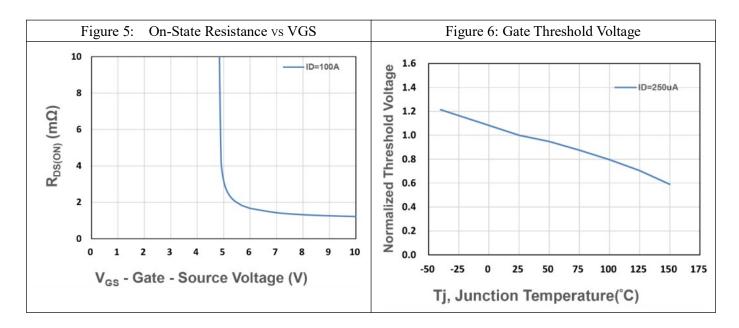

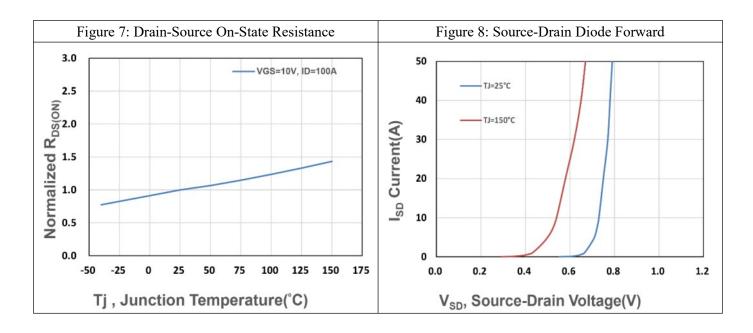

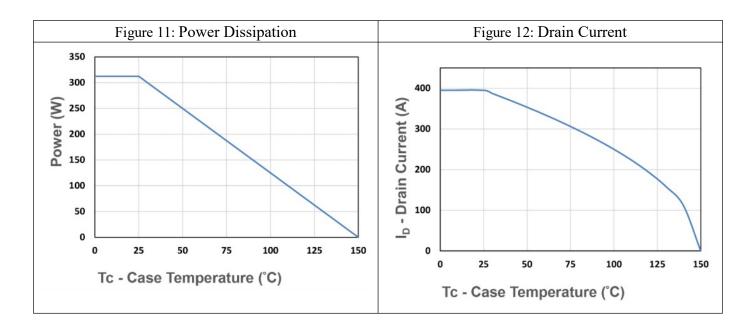

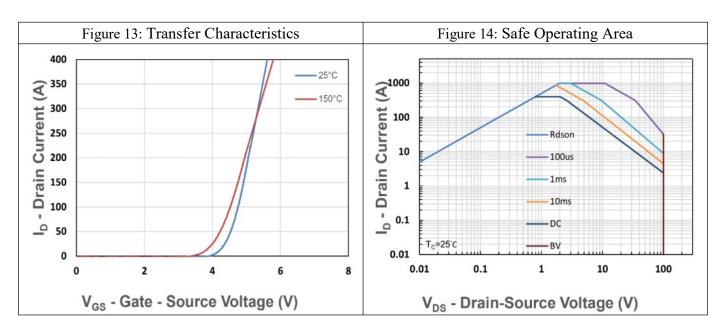

## **Typical Performance Characteristics**

### VFTV010R013NA

### VFTV010R013NA

## VFTV010R013NA

VFTV010R013NA

#### **NOTICE**

Hangzhou VMD Semiconductor Co., Ltd (VMD) reserves the right to make changes without notice in order to improve reliability, function or design and to discontinue any product or service without notice. Customers should obtain the latest relevant information before orders and should verify that such information is current and complete. All products are sold subject to VMD's terms and conditions supplied at the time of order acknowledgement.

VMD, its affiliates, agents, and employees, and all persons acting on its or their behalf, disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product. VMD disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify VMD's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

VMD warrants performance of its hardware products to the specifications at the time of sale, testing, reliability and quality control are used to the extent VMD deems necessary to support this warrantee. Except where agreed upon by contractual agreement, testing of all parameters of each product is not necessarily performed.

VMD does not assume any liability arising from the use of any product or circuit designs described herein. Customers are responsible for their products and applications using VMD's components. To minimize risk, customers must provide adequate design and operating safeguards.

VMD does not warrant or convey any license to any intellectual property rights either expressed or implied under its patent rights, nor the rights of others. Reproduction of information in VMD's data sheets or data books is permissible only if reproduction is without modification or alteration. Reproduction of this information with any alteration is an unfair and deceptive business practice.

VMD is not responsible or liable for such altered documentation. Resale of VMD's products with statements different from or beyond the parameters stated by VMD for that product or service voids all express or implied warrantees for the associated VMD product or service and is an unfair and deceptive business practice.

All Rights Reserved.

#### Via-Media Semiconductor Limited Company

### http://www.vmdsemi.com

#### **Main Sites:**

#### - Headquarters

Hangzhou Via-Media Semiconductor Co., LTD. 1305-1306, Building 71, No. 90, Wensan Road, Xihu District, Hangzhou, Zhejiang Province, P.R. China Tel: +86-0571-8515 0563

#### - Shanghai

Shanghai R&D Center. 1506~1508, Xinyin Building, 888 Yishan Road, Shanghai, P.R of China Tel: +86-021-54201999

#### - Xi'an

Xi'an R&D Center 1703B, Building A, Greenland Center, Jinye Road, High-Tech Zone, Xi'an, Shaanxi, P.R of China

#### - Chengdu Office

Chengdu Winhi Semiconductor Co., LTD. Floor 15, Building 5, No. 171, Hele 2<sup>nd</sup> Street, Chengdu, Sichuan Province, P.R. China Tel: +86-028-8505 0771

#### - Shenzhen

Shenzhen Sales Center. 17B, No.1 Phoenix Building, 2008 Shennan Road, Shenzhen, P.R of China Tel: +86-0755-82570682